# ■10 群 (集積回路) - 1 編 (基本構成と設計技術)

# 2章 基本構成

(執筆者:編幹事団) [2009年4月受領]

### ■概要■

この章では、設計対象である集積回路をその構成要素の視点から概観する.

### 【本章の構成】

2-1 節 "ディジタル回路"では、メモリ以外のディジタル回路を、用途及び製造形態で分類して概観するとともに、それらを構成する際によく用いられるモジュール(部品)を分類して概説する.

また, 2-2 節 "メモリ"では、半導体メモリを分類・概観し、2-3 節 "アナログ回路"では、基本的なアナログモジュールの設計課題を概説する.

2-4 節 "配線"では、モジュールを接続するための配線を、信号配線、クロック配線、及び電源配線に分類し、それらの設計課題を概説する.

2-5 節 "実装技術"では、チップの実装(packaging)方式を、1パッケージに1チップを搭載するシングルチップパッケージ技術と、複数のチップを搭載するマルチチップパッケージに分類し、その設計課題を概説する.

## ■10群 - 1編 - 2章

# 2-1 ディジタル回路

(執筆者:山田 節) [2008年7月受領]

## 2-1-1 チップレベルの分類

## (1) マイクロプロセッサ

初期のコンピュータは、複数の半導体チップを用いた構成で演算処理を行っていたが、これを一つのチップ上に集積した中央演算装置(CPU: Central Processing Unit)がマイクロプロセッサである。マイクロプロセッサの基本的な処理は、メモリに記憶されたプログラム(命令)を読み込み(フェッチ)、フェッチした命令を解読(デコード)し、デコード結果に基づいて記憶装置や入力装置からデータを受け取り、データを命令どおりに実行(演算処理)をして、この結果を記憶装置や表示装置に出力する、ことにより行われる.

マイクロプロセッサには、複合命令セットコンピュータ(CISC: Complex Instruction Set Computer)と、縮小命令セットコンピュータ(RISC: Reduced Instruction Set Computer)の二つの大きな方式(アーキテクチャ)がある.処理性能を上げるために、複数語命令を同時実行する VLIW(Very Long Instruction Word)、SIMD(Single Instruction Multiple Data)/MIMD(Multiple Instruction Multiple Data),スーパースカラ方式などのアーキテクチャも利用されてきている.更に、一つのチップ上に複数のプロセッサを搭載するマルチプロセッサも主要なマイクロプロセッサとなってきている.

マイクロプロセッサは、ワークステーションやパーソナルコンピュータなどの計算機や産業機器などの制御で多く使われてきたが、携帯電話、情報家電、家庭用ゲーム機などのディジタル製品にも広く用いられてきた。現在では、急速に自動車のエンジン制御を含む各種車載制御に広く利用されている。

#### (2) PLD (Programmable Logic Device)

設計者がプログラムで LSI 内部にアレイ状に配列された論理回路を容易に定義・変更することにより機能が実現できる LSI である。納期の短い少量多品種生産に向いた集積回路であるが、量産品にも利用されている。プログラム方法には、SRAM (Static Random Access Memory) セル方式、EPROM (Erasable Programmable Read Only Memory) 方式、フューズ方式、アンチフューズ方式などがある。PLD には、AND、OR ゲートと共にプログラム可能な PLA (Programmable Logic Array)、OR ゲート固定で AND ゲートのみプログラム可能な PAL (Programmable Array Logic)、小規模な論理ブロックをチップ内で配線接続する FPGA (Field Programmable Gate Array) などがある。

初期の PLD は、動作中には回路変更ができなかったが、動作中にも回路を変更することができるリコンフィギャラブルデバイス(Reconfigurable Device)も開発されている.

### (3) ASSP (Application Specific Standard Product)

半導体ベンダが主体となって設計や開発を行った特定用途向けに機能を特化した標準 LSI である。半導体ベンダ側で標準品としてラインアップして市場に提供されるタイプの LSI のうち、例えば、通信用、映像用、電源用などといったように、ある程度システムを想定してつくられたタイプの LSI をさす。画像処理専用 DSP、オーディオ用 DSP といった機能を特化した DSP も ASSP に含まれる。 ASIC と異なりユーザが設計する必要がないために、開発費

や開発期間において有利である。商品の差別化にあまり影響のない標準規格をサポートする LSI などにしばしば用いられる。

#### (4) ASIC (Application Specific Integrated Circuit)

ロジック LSI の種類一つで、低消費電力化、動作速度向上、小型実装などを目的に顧客が顧客側の仕様で設計を行い、それを半導体ベンダが LSI 化した特定用途向けに複数の機能回路を集積した LSI である。半導体ベンダが自社の LSI 設計環境に基づいたライブラリや再利用可能な機能ブロック (IP: Intellectual Property) を提供し、顧客側でこれを用いて回路設計を行うものである。ASIC には、(i) 基本論理セルや入出力回路などをシリコンウェア上に下地としてあらかじめ形成しておき、顧客の設計に従って基本回路間の配線だけを行うことで短期に LSI を実現できるゲートアレイ、(ii) ゲートアレイの下地の一部にレイアウト設計済みの高機能セル(マクロセル、メガセル)を埋め込み、そのほかはゲートアレイと同じ手法を用いるエンベディドアレイ、(iii) 高機能マクロとこれ以外の回路を、下地から論理ゲートと配線を最適に組み合わせてつくり込むセルベースなどがある。また、シリコンウェアの下地回路であるマスタに、入出力インタフェース、クロック生成回路などの主要な機能ブロックを埋め込み、配線層の一部を共通化することにより、開発期間の短縮と開発費を低減したストラクチャード ASIC も開発されてきている。ASIC に対して半導体ベンダが仕様を考えて設計・製造するタイプの LSI を ASSP と呼ぶ。

ASIC は半導体製造の微細化技術の急激な進歩に伴い、一つの半導体チップ上に搭載可能なゲート数が飛躍的に増加している。これを受けて、顧客側での設計時に、半導体ベンダ側から提供される機能ブロック(マクロセル)を利用する傾向がますます強くなっている。マクロを利用することで、標準的な処理を行う部分には動作実証された回路を利用でき、設計工数を削減することができる。最先端のマイクロプロセッサや DRAM などもマクロとして提供されている。

#### (5) システム LSI

SoC (System on a Chip) とも呼ばれ、マイクロプロセッサ、メモリ、特定分野向け信号処理回路、通信インタフェース回路、センサ、及びアナログ回路などの集積回路だけでなく、マイクロプロセッサ上で動作するオペレーティングシステムやアプリケーションプログラムなどのソフトウェアも一つのチップ上に搭載した特定システム向け LSI がシステム LSI である. ASIC との違いは、製品のすべての機能を LSI 上に搭載することであり、開発には、応用分野の技術を集積した市場開拓、企画、設計、製造の一貫性が求められる.

システム LSI の性能は、設計の技術力が重要であり、システムそのものの設計と LSI 設計を同時に行うこと、システム検証、ハードウェア・ソフトウェアのコデザイン、更には微細化に伴う物理現象を考慮したフィジカル設計にも立ち入る必要がある。システム LSI には、システムの小型化、低消費電力化、高性能化、高機能化、低価格化、短期設計化の少なくとも 1 項目が期待され、設計工数も増大している。この工数短縮のために、SystemC などのシステム記述言語を用いた高位合成技術や IP (Intellectual Property) を再利用する設計手法が一般化してきている。

システム LSI は、情報家電や産業機器の中核部品としてではなく、電子マネーや電子商取引などの経済システム、及び ITS (Intelligent Transport Systems) に代表される高度道路交通システムなどの社会システムを支える基盤情報技術としての重要性も高まっている.

## 2-1-2 チップ内モジュール

## (1) ゲート

論理回路は、ディジタル信号を取り扱うために、信号として電位が高い「H」か、低い「L」が重要であり、アナログ信号のようにすべての電圧レベルでの忠実度を必要としなく、「H」を「1」、「L」を「0」として、2値を用いたブール代数を用いて論理演算を行う。この演算は、基本的な組合せ回路である論理積(AND)、論理和(OR)、否定(NOT)などの論理ゲートを組み合わせて実現している。

# (2) バッファ

集積回路内部もしくは集積回路間において、データを送受信する際に、入力、信号処理、 出力などのタイミングが設計と異なる場合に、この時間差を調整するために用いる回路である。

#### (3) ラッチ/フリップフロップ

順序回路の基本素子であり、順序回路の内部状態をディジタル処理の基本となる「1」または「0」の状態に保持するのに用いられる. ラッチ/フリップフロップには、SR (Set Reset)、D (Delay)、T (Toggle)、JK などの種類がある. 電源投入時には、ラッチ/フリップフロップは、ランダムに「1」または「0」の状態になるので、パワーオンリセットを用いて、電源投入時に出力値が任意に「1」または「0」になるようにしている.

#### (4) レジスタ

ビット情報を記憶するために、フリップフロップなどを並べて構成した回路がレジスタであり、複数ビットの同時書込みや読出しができる。特にマイクロプロセッサ中には、演算結果を記憶するアキュムレータやメモリアクセスを行う際にアドレスを指定するアドレスレジスタなどの多数の専用レジスタがある。

#### (5) 入出力回路

ディジタル回路と外部デバイスを接続するために、信号の入出力に用いるディジタルのインタフェース回路が入出力回路であり、集積回路では、チップの周囲に配置され電極パッドなどで構成されている.「1」または「0」に相当する電圧を、チップ外に出力する回路、チップ外から入力する回路、もしくは入出力できる回路である.

#### (6) クロック生成回路

ディジタル回路は、クロック信号でチップ内の回路の同期を取りタイミングを合わせて動作を行う。このクロックを発生させる回路がクロック生成回路であり、チップ内全体でクロック信号の伝播時間に遅延を生じさせない、更に LSI 内部と外部でも遅延を発生させないことが必要である。クロック生成回路には、発信回路の出力をリファレンスクロックと比較して発信特性を制御する PLL (Phase-Locked Loop)、PLL の発信回路を LSI 上の遅延回路で置き換えた DLL (Delayed Locked Loop)、非帰還回路による制御方式を用いて周波数制御に用いられる SMD (Synchronous Mirror Delay) などがある.

# 2-2 メモリ

(執筆者: 竹内 健) [2008年5月受領]

### 2-2-1 メモリの分類と構成

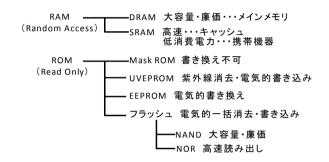

図 2・1 は半導体メモリを分類したものである。半導体メモリは、RAM(Random Access Memory)と ROM(Read Only Memory)に大別される。RAM はランダムアクセスが可能であるが、揮発性であるため電源を切ると情報を失う。一方、ROM は読み出し専用あるいは、書き込みや消去にマイクロ秒以上の長時間を要し、書換え単位が数キロバイトサイズのページあるいは数百キロバイトサイズのブロックという制約がある。ROM は不揮発性すなわち電源を切っても情報を失わない利点がある。RAM と ROM の利点を併せもち、不揮発性でありながらランダムアクセス可能な新規メモリが近年提案されている。

図 2・1 半導体メモリの分類

#### 2-2-2 DRAM

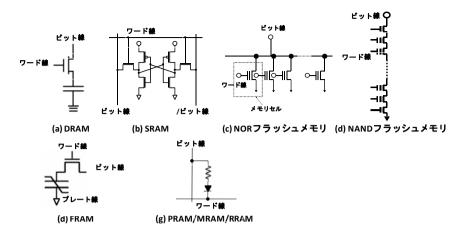

DRAM (Dynamic RAM) は図 2・2 に示すようにトランジスタと容量で構成される. SRAM に比べて速度は遅いものの、構成素子数が少なく、面積が小さいという利点がある. 低コストの利点を生かしてパソコン・ワークステーションなどの計算機からディジタルカメラ・携帯電話などの携帯機器まで幅広い機器の主記憶として使用されている. DRAM は容量に蓄えた電荷がトランジスタのチャネルやドレインの PN 接合などを介してリークするため、定期的 (1ms 程度ごと) に容量に電荷を再充電するリフレッシュ動作が必要になる. DRAM は容量がシリコン基板の溝に形成されるトレンチ型と、トランジスタよりも上の配線層に形成されるスタック型に大別される.

#### 2-2-3 SRAM

SRAM (Static RAM) はフリップフロップ回路とトランスファゲートの 6 素子で構成される. DRAM に比べて素子数が多いため、面積が大きく価格も高い. 高速であること、リフレッシュが不要で使いやすいことからマイクロプロセッサ内のキャッシュメモリなどに使用されている. またリフレッシュが必要な DRAM と比べて低電力化できることに着目して、携帯端末にも使用されている.

図2・2 各種半導体メモリの等価回路

# 2-2-4 不揮発性メモリ

不揮発性メモリには、読出し専用の MROM(Mask ROM)と電気的に書換え可能な PROM (Programmable ROM) がある。MROM はチップの製造工程で情報をあらかじめ書き込み、製造後は書換えができない。PROM は大別して、バイト単位で書換えが可能な EEPROM (Electrically Erasable PROM)、ページ単位あるいはブロック単位で書換えが可能なフラッシュメモリがある。NOR フラッシュメモリではホットエレクトロン注入、NAND フラッシュメモリではトンネル効果を利用してフローティングゲートに電子が注入され、書込み動作が行われる。NOR フラッシュメモリは読出しが高速であることを活かして、携帯電話・セットトップボックス・PC(Personal Computer)などの BIOS(Basic Input/Output System)やプログラム格納に使われている。NAND フラッシュメモリは 32~64 個のメモリセルを直列接続して構成される。コンタクト領域を省略できるため、小面積・大容量を実現できる。更に書込みが高速であることから、携帯電話、音楽プレーヤ、ディジタルカメラ、PC などのストレージとして使用されている。

#### 2-2-5 システムメモリ

上記のメモリは任意のアドレスに対して、該当するアドレスに記憶するデータをアクセスするものであった.一方、システムの高性能化のために、特殊な記憶を行うシステムメモリがある.連想メモリは集積密度を犠牲にする一方、検索動作の高速化を図っている.また、マルチポートメモリでは複数のワード線を同時に選択することでデータの読出しの高速化を図っている.

#### 2-2-6 新メモリ

不揮発性でありながらランダムアクセスが可能な様々なメモリが提案されている。トランジスタと強誘電体膜で形成された容量で構成される FRAM (Ferroelectric RAM) は,低消費

電力を活かしてスマートカードに使用されている。また、ダイオードと抵抗素子で構成されるメモリとして、PCRAM (Phase Change RAM)、MRAM (Magnetoresistive RAM)、RRAM (Resistance RAM) が提案されている。PRAM はカルコゲナイド物質で抵抗を構成し、結晶とアモルファスの相変化で記憶する。MRAM は MTJ (Magnetic Tunnel Junction)素子で抵抗を構成し、磁性の原理により記憶する。新メモリは小面積・三次元積層が可能なことから、DRAM の置換えやフラッシュメモリの置換えなど様々な応用が期待されている。

# 2-3 アナログ回路

(執筆者:石黒仁揮) [2009年1月受領]

テクノロジーのスケーリングとともに MOSFET の動作速度が向上し、無線通信用トランシーバ回路などの高周波アナログ回路も CMOS で実現できるようになった。 CMOS で高周波を含むアナログ回路を実現することで、大規模ディジタル回路と混載され、ワンチップトランシーバ LSI も実現されている。このように、CMOS アナログ回路の重要性とその適用範囲が急速に増大している。しかしながら、素子の微細化とともに、電源電圧の低下、素子特性のバラツキ増大、MOSFET の固有利得の低下など、アナログ回路設計にとって考慮すべき項目も増えている。本節では、CMOS アナログ集積回路の基本構成要素と先端プロセスを用いた回路設計で考慮すべき点を概説する。

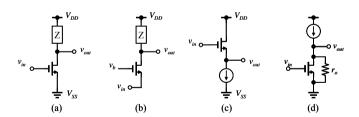

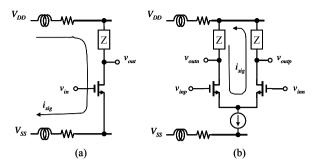

## 2-3-1 MOS 增幅回路

MOSFET を用いた増幅回路は三つの基本構成から成り立つ. ソース接地回路 (図  $2\cdot 3(a)$ ), ゲート接地回路 (図  $2\cdot 3(b)$ ), ドレイン接地回路 (ソースフォロワー) (図  $2\cdot 3(c)$ ) である <sup>1)</sup>. ソース接地回路において、MOSFET のトランスコンダクタンスを  $g_m$ 、出力ノードのインピーダンスを Z とすると低周波電圧利得は  $g_m Z$  となる. 電流源を負荷とすると (図  $2\cdot 3(d)$ ), Z は MOSFET の出力抵抗  $r_o$  となり利得は  $g_m r_o$  となる. これは、一つの MOSFET で達成できる最大の電圧利得となり固有利得と呼ばれ、バイアス条件に依存するが 30dB 程度である. また,ゲート入力容量を  $C_g$  とすると,電流遮断周波数は  $f_T = g_m/C_g$  となる. 先端デバイスにおいては、電流周波数が向上してきているが、短チャネル効果の影響で  $r_o$  が低下してきており、

固有利得はテクノロジーのスケーリングとともに減少してきている2.

図2・3 MOSFET 基本増幅回路

ゲート接地は、ゲートを基準電位としてゲートソース間に信号を印加して、ドレインから信号を取り出す。入力インピーダンスが $g_m^{-1}$ となり、低入力インピーダンスを実現できる。また、ソース接地回路の出力をゲート接地回路に接続したものをカスコードと呼び、高い電圧利得及び入出力間アイソレーションの実現のためにしばしば用いられる。ドレイン接地はドレインを基準電位として、ドレインゲート間に信号を印加してソースから出力する。高入力インピーダンス、低出力インピーダンスのバッファとして、また、レベルシフト回路として利用される。

複雑に見える回路も基本的には飽和領域で動作する上記三つの基本回路の組合せで実現される。

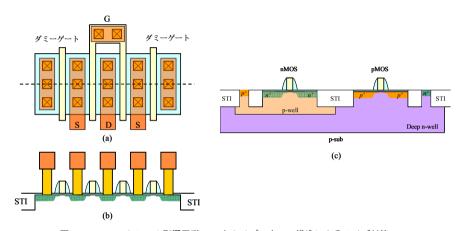

アナログ回路においては、素子特性バラツキが回路の性能に大きな影響を与える。 微細化と共にサイズ、不純物濃度のバラツキが相対的に増大している  $^{3)}$  が、それに加えて STI ストレスがチャネル移動度に与える影響が増えてきている。 図  $^{2\cdot4}(a)$ ,(b)のように、MOSFET の両側にダミーゲートを配し、ゲート加工のバラツキと共に、チャネルと STI の距離をある程度離すことで STI ストレスの影響を抑えることがよく行われる  $^{4\sim5}$ . また、大規模なアナログ・ディジタル混載 LSI において、基板を介したディジタルスイッチングノイズの伝播を抑えるために、図  $^{2\cdot4}(c)$ に示すような Deep N-well を用いた素子分離が用いられることも多い.

図2・4 STI ストレスの影響回避(a)(b)とトリプルウェル構造によるノイズ対策(c)

#### 2-3-2 差動増幅回路

先端 CMOS を用いたアナログ回路設計においては、テクノロジースケーリングに伴う電源電圧の低下によりダイナミックレンジの確保が困難になっている。また、ディジタル回路と混載されることが多くなり、そのスイッチングノイズの影響が問題となってきている。

これらの影響を受けないようにするために、アナログ集積回路においてはしばしば信号を 差動形式で扱う. そのための差動回路の特徴としては、

- ・単相信号に対して、信号振幅を2倍にすることができ、線形性を改善することができる。

- ・偶数次ひずみを大きく低減することができ、ダイレクトコンバージョン方式無線トランシーバなどの偶数次ひずみが重要な回路で有利である。

- コモンモードノイズを除去することができ、ディジタルスイッチングノイズ等の影響を排除しやすい。

- ・交流信号電流が回路内部で閉じているため、電源、グランドの寄生インピーダンスの影響を受けにくい(特に高周波回路で重要.図2・5参照).

ただし、対称性を考慮せずにレイアウトを行うと、差動信号線に付加される寄生素子のバランスがくずれ、上記の特徴のうち特に2,3番目の利点が損なわれる.

図2-5 電源グランド寄生インピーダンスが単相回路(a)と差動回路(b)に与える影響

## 2-3-3 コンパレータ回路

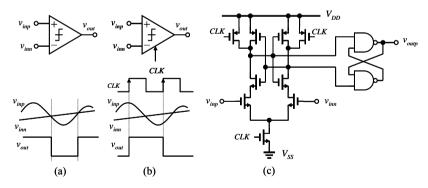

コンパレータは増幅率の極めて高い増幅器と見なすことができ、データコンバータなどで重要な役割を果たす。オペアンプと異なり帰還をかけないため、アンプの段数を増やすことによって、利得、動作速度を改善することができる $^{6}$ . コンパレータには入力と参照電位の差を常時比較する方式(図  $2\cdot6(a)$ )と、クロックの立ち上がりエッジに同期して比較を行う方式(図  $2\cdot6(b)$ )がある。AD 変換器は通常クロックに同期してデータ変換を行うため、コンパレータもクロック同期型が用いられる場合が多い。また、図  $2\cdot6(c)$ のように、再生増幅の機能をもったセンスアンプにデータ保持用のラッチを加えた方式 $^{7}$ は、クロック遷移時にのみ電力を消費するため、低電力化に向いた方式であり頻繁に使用される。

図2.6 コンパレータの動作. (a)非同期. (b)クロック同期. (c)クロック同期方式の回路

入力換算オフセット電圧も精度を決める重要な指標である。オフセット軽減のために、各種オフセットキャンセル手法が考案されている<sup>6</sup>. 特に、クロック同期方式においては、クロックの比較フェーズ以外にオフセットを検出してキャパシタに保持し、オフセットをキャンセルする方式がよく用いられる(ただし、この場合は安定性に対する考慮が必要となる).

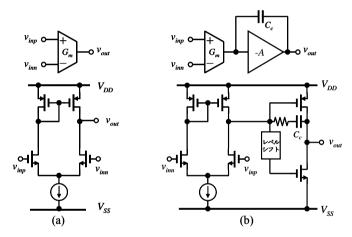

#### 2-3-4 オペアンプ

MOSFET の微細化に伴うトランジスタの動作周波数の向上によって、GB 積が数 GHz といった非常に帯域の広いオペアンプが実用化されている。ただし、ユニティゲインは向上してきているが、固有利得の減少とともに DC 利得を確保することが困難になってきている。スイッチドキャパシタ回路のような容量性負荷に対しては、位相補償が不要で帯域の広い、図2・7(a)のような一段のオペアンプ(オペレーショナルトランスコンダクタンスアンプ:OTA)が用いられる。ゲインブースティング付きの折り返しカスコードを用いることで、電源電圧及び MOSFET の固有利得の低減に対処して高い DC 利得を得る。抵抗性負荷においては、図2・7(b)のような2 段以上のオペアンプが利用されるが、位相補償用の容量が必要となり、1段アンプに比べて動作帯域が狭くなる。

図2・7 は単相出力形式であるが、集積回路においては、差動入力差動出力方式のオペアンプが用いられることが多い。また、2 段以上の方式では、低い電源電圧で、より広い出力レンジ (場合によっては入力も)を確保するためにクラス AB 方式の出力段がよく用いられる 6.

図2・7 単相オペアンプの回路構成例(a)1段,(b)2段

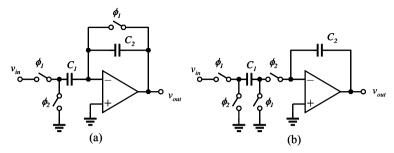

## 2-3-5 スイッチトキャパシタ回路

もともと CMOS アナログ回路は MOS が理想的なスイッチに近いことから,スイッチトキャパシタ回路を用いた離散時間信号処理(フィルタ,データコンバータ)に適していた. **図 2・8**(a),(b)は,スイッチトキャパシタ回路を用いた増幅器及び積分器である.サンプリングフェーズでクロック $\phi$ が供給されたスイッチが閉じ, $C_1$ に信号がサンプリングされる.増幅フェーズでクロック $\phi$ 2が供給されたスイッチが閉じ, $C_1$ の電荷が $C_2$ に転送され, $C_1/C_2$ に比例した利得がかかり出力される.積分器では $C_2$ の電荷をリセットしないため,過去にサンプリングした電荷が蓄積され積分動作を行う.増幅率の場合は増幅率が容量比で決まり,積分器の場合には積分利得が容量比とクロック周波数で決まるため,精度を上げることが可能である.

また、最近では素子微細化とともにスイッチング動作が高速になり、オペアンプを使用しないスイッチドキャパシタが RF 帯域における離散時間信号処理に適用されてきている 8~9).

電源電圧の低下に伴う MOS スイッチのオン抵抗増大に対処するため、ゲート制御電圧を増 大させるブートストラッピング回路などが使用される。

図 2·8 オペアンプを用いたスイッチドキャパシタ回路. (a) 増幅器. (b) 積分器

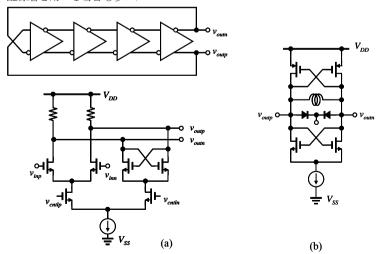

## 2-3-6 発振回路

プロセッサ,通信用 LSI における重要な回路ブロックとして,クロック生成あるいは周波数変換のために用いられる発振器がある.通常 PLL の中に組み込んで使用するため,制御電圧信号で発振周波数が調節できる VCO が用いられる.プロセッサのクロック生成用には周波数可変域の広いリング発振器が主流である(図  $2 \cdot 9(a)$ ).ただし,電源ノイズ耐性を高めるために,通常,差動遅延回路で構成される.また,通信用途の発振器では図  $2 \cdot 9(b)$ のような位相ノイズ特性の良い LC 発振器が使われる  $^{10}$ ).動作周波数の増大とともに,インダクタが小型になり,オンチップのスパイラルインダクタが利用されるようになってきている.オンチップインダクタは配線抵抗,及び,容量結合による基板に流れる変位電流と磁界結合による渦電流でロスが生じ Q 値が低下する.特に配線抵抗が大きな影響を与えるため,通常よりも厚い配線層を用いる場合も多い.

図2・9 発振回路例. (a)リング発振器, (b)LC 発振器

#### ■参考文献

- 1) Behzad Razavi, "Design of Analog CMOS Integrated Circuits," McGraw-Hill, 2003.

- 2) S.S. Suryagandh, M. Garg, and J.C.S. Woo, "A device design methodology for sub-100-nm SOC applications using bulk and SOI MOSFETs," IEEE Trans. on Electron Devices, vol.51, no.7, pp.1122-1128, Jul. 2004.

- P.R. Kinget, "Device mismatch and tradeoffs in the design of analog circuits," IEEE J. Solid-State Circuits, vol.40, no.6, pp. 1212-1224, Jun. 2005.

- 4) H. Kim, J. Kim, C. Chung, J. Lim, J. Jeong, J.H. Joe, J. Park, K. Park, H. Oh, and J.S. Yoon, "Effects of Parasitic Capacitance, External Resistance, and Local Stress on the RF Performance of the Transistors Fabricated by Standard 65-nm CMOS Technologies," IEEE Trans. on Electron Devices, vol.55, no.10, pp. 2712-2717, Oct. 2008.

- 5) B.P. Wong, A. Mittal, Y. Cao, and Greg Starr, "Nano-CMOS Circuit and Physical Design," Wiley, 2004.

- 6) Roubik Gregorian, "Introduction to CMOS Op-Amps and Comparators," Wiley, 1999.

- A.G.M. Strollo, D.De Caro, E. Napoli, and N. Petra, "A novel high-speed sense-amplifier-based flip-flop," IEEE Trans. on Very Large Scale Integration (VLSI) Systems, vol.13, no.11, pp.1266-1274, Nov. 2005.

- J.K. Fiorenza, T. Sepke, P. Holloway, C.G. Sodini, and Hae-Seung Lee, "Comparator-Based Switched-Capacitor Circuits for Scaled CMOS Technologies," IEEE J. Solid-State Circuits, vol.41, no.12, pp.2658-2668, Dec. 2006.

- K. Muhammad, R.B. Staszewski, and D. Leipold, "Digital RF processing: toward low-cost reconfigurable radios," IEEE Communications Magazine, vol.43, no.8, pp.105-113, Aug. 2005.

- T.H. Lee, and A. Hajimiri, "Oscillator phase noise: a tutorial," IEEE J. of Solid-State Circuits, vol.35, no.3, pp. 326-336, Mar. 2000.

# 2-5 実装技術

(執筆者:本多 進) [2008年11月受領]

これまで DRAM を中心とした IC チップ集積度の伸びは 3 年で 4 倍とされてきた Moore の 法則が微細化の限界に近づきつつあり、More Than Moore が叫ばれる中で、1 チップの SoC に替わってマルチチップの MCP(Multi-Chip Package)や SiP(System in Package)が急増してきた。このため今世紀に入って IC チップのパッケージング開発が急速に進み、革新的技術 も登場して新実装構造による展開が進んでいる。

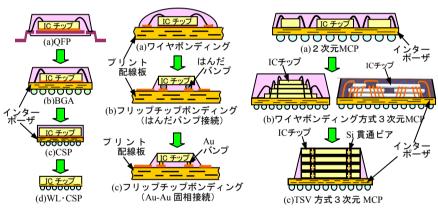

## 2-5-1 シングルチップパッケージ

1 チップを封入したパッケージは、IC の集積度の増大とともに端子数が急増して狭ピッチ化が避けられず、図 2・10 のように周辺 4 方向引き出しの QFP(Quad Flat Package)から端子をパッケージ下面にグリッドアレイ状に配置した BGA(Ball Grid Array)、それを更にチップサイズまで近づけた CSP(Chip Scale Package)、更に最近ではウェハ工程でパッケージまで仕上げる WL・CSP(Wafer Level・Chip Scale Package)が出現してきた.

**図2·10** シングルチップ パッケージの小型化動向

図 2·11 ベアチップの プリント配線板への ボンディング動向

図 2·12 マルチチップパッケー ジの2次元実装→3次元実装 による小型, 薄型化動向

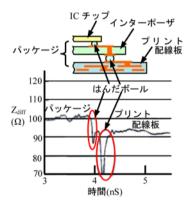

こうしたベアチップ近似のパッケージの出現でプリント配線板へのベアチップ実装は減少傾向にあるが、コストや省スペース面から小型携帯機器には依然として採用が続いている。これには図 2・11 のように、チップの入手が容易な点から同図(a)のワイヤボンディング実装が多いが、ワイヤの占有面積が大きく、ループ形状で伝送特性が異なるなどのため、超小型機器や高速チップには(b)のはんだバンプによるフリップチップ実装が増加している。しかしGHz 帯の高速信号伝送ではインターポーザ(Interposer)のめっきスルーホール(PTH: Plated Through Hole)やバンプ接続部が電気的な不連続点となり、図 2・13 のようにインピーダンス不整合 1) が生じやすいので、これらを減らす構造が必要となる。ワイヤボンディングで PTH

を回避して信号劣化を防ぐ例も見られ、必ずしもワイヤボンディングが問題とは云えないが、 その際もワイヤ長を最短に抑える必要がある。

また、 $50\mu$  m を切る狭ピッチ品では、図  $2\cdot 4$ (b)のはんだバンプの溶融接続より同図(c)の Au バンプによる基板 Au 電極への Au-Au 固相接合が好ましい. バンプ部の接続抵抗低減にも役立つ.

## 2-5-2 マルチチップパッケージ --2 次元実装から 3 次元実装へ--

複数チップを1パッケージに集積して高機能化,モジュール化する動きは図2・5・3(a)のような2次元実装主体で伸びてきたが、実装効率や配線長による性能面での問題があった。

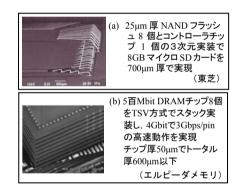

そこで省スペース化に向けて、IC チップの 3 次元実装が今世紀初めから実用化された. 当 初は図 2・12(b)左に示すような単純な構造であったが、その後、積層法やボンディング法の改良が進み、現在では同図右の複雑な構造の製品化も進んでいる. ワイヤ長は長くなるが省スペース化や薄型化を狙って大容量メモリモジュールなどが製品化されている(図 2・14(a)).

**図 2・13** はんだバンプ接続部でのインピーダンス不整合の例<sup>1)</sup>

図 2・14 超薄 IC チップを使用し、ワイヤボ ンディングと TSV によりスタックした超薄 型メモリの例

更にワイヤレスで IC チップどうしを接続する方法が開発された. Si チップに貫通孔を明け、内部を Cu めっきで充填し、チップ裏面に電極を出して( $TSV^2$ ): Through Si Via)積層する方法である。配線が短く高速チップ実装に好適である(図  $2\cdot14(b)$ ). TSV 加工のコスト低減が課題であるが、一部製品化も始まり、超高速 MPU とメモリの組合せなど、性能向上への期待が大きい。

一方, これらの 3 次元実装には Si チップ裏面の研削, 薄片化技術の寄与が大きい. 既に  $700\mu$ m厚前後のチップを  $50\mu$ m 厚以下に薄片化する技術も開発され,上の図 $2\cdot14(a)$ の  $25\mu$ m 品はすでに製品化されており, 更に  $18\mu$ m厚 16 チップで 16GB 品の製品化も進んでいる.

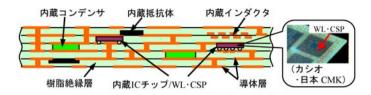

更に最近では、小型、薄型、軽量化や配線長短縮による回路性能向上を狙って、能動・受動部品類を配線板に内蔵する動きも出てきた<sup>3</sup>. IC は WL·CSP ないしベアチップが他の受動部品類とともに樹脂系のインターポーザやマザーボードに内蔵される(図 2·15). ここで

はもはやパッケージや配線板の姿はなく、部品類と配線板が一体化した機能体となる. このように IC チップ実装は今、新たな展開方向にあり、新構造出現への期待が大きい.

図2・15 能動・受動部品内蔵配線板の構造

## ■参考文献

- 1) 須藤俊夫, "エレクトロニクス実装学会関西支部第3回技術講演会資料,"12月 2006.

- 高橋健司, "超高密度三次元 LSI チップ積層実装技術の研究開発,"第4回電子SI研究報告会,pp.39-51, 2003.

- 3) 本多進, "基板上3次元実装から基板内3次元実装への動きを探る," エレクトロニクス実装学会関西 支部第4回技術講演会資料,2月2008.