## 13章 符号化実現

(執筆者:長沼次郎) [2013年3月受領]

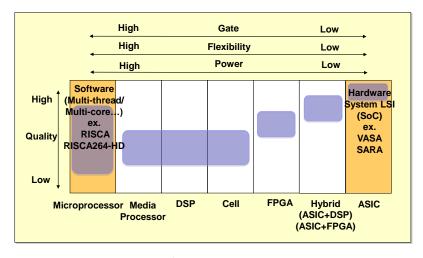

画像(映像)符号化の符号化実現は、近年では、家庭用のビデオカメラからデジタル放送 局用の送出装置まで、また PC ベースの TV 会議システムから蓄積メディアのオーサリング システムまで、その関連する範囲は非常に幅広い、例えば、映像符号化国際標準の MPEG-2<sup>1)</sup> や H.264/AVC<sup>2)</sup> の HDTV (1920×1080) のインタレース画像 (1080i) の符号化 (エンコード) 処理を考えた場合, HDV<sup>3)</sup> 準拠や AVCHD<sup>4)</sup> 準拠の民生カメラ組込み用であれば 1080i で 1 W 以下, 放送プロ用であれば 1080i で 5 W 以下の消費電力のハードウェア (SoC: System on a Chip) が開発されている. 一方, 近年のマイクロプロセッサのマルチコア化 5 などによる高速化に よりソフトウェアでも可能となってきたが、1080iを実現するとその電力は100Wを超える. これらの中間的な解として, DSP(ディジタル信号処理プロセッサ)やメディアプロセッサ を利用するもの、Cell<sup>6</sup> などのゲームプロセッサを利用するもの、また FPGA (フィールドプ ログラムゲートアレイ)を利用するもの、これらを組み合わせたものなど、数 W~数十 W の様々な実装が可能である。映像符号化実現技術の設計問題のトレードオフは、図 13・1 に示 すように、演算量(またはゲート規模も同等)、映像品質、柔軟性、消費電力などの与えられ た条件の下で、如何に最適なハードウェア/ソフトウェア構成(アーキテクチャ)を導出す るかである. ここでは映像符号化実現について, ハードウェア及びソフトウェアの実現技術 の観点から概観する.

図 13・1 映像符号化実現技術のトレードオフ

## 13-1 映像符号化ハードウェア

(執筆者:長沼次郎) [2013年3月受領]

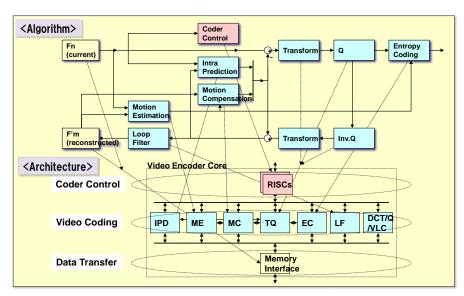

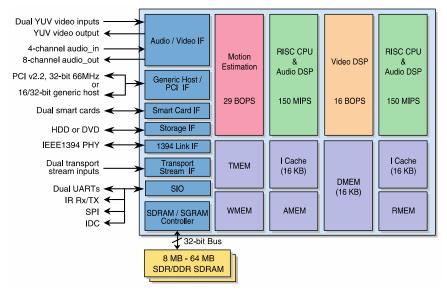

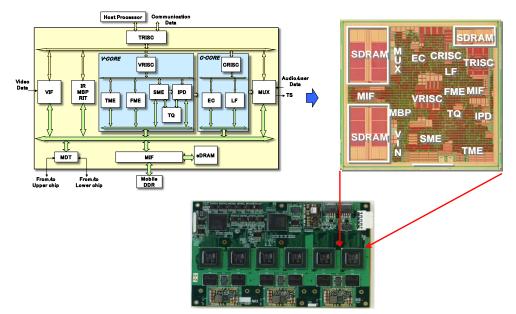

映像符号化のハードウェア実現では、対象となる映像符号化標準の処理アルゴリズムのもつ並列性を如何に実現し、ハードウェアのアーキテクチャへマッピングするかが設計問題である. H.264/AVC のアルゴリズムと多くの専用チップで採用されているマクロブロック (MB) パイプラインアーキテクチャ<sup>n</sup> のマッピングの概要を図 13・2 に示す 8). 本アーキテクチャでは大きく三つのレイヤーで構成されており、(1)映像符号化の最も上流のフレーム単位でのレート制御(RC)などを行うコントロールレイヤー、(2)マクロブロック (MB)単位での要素演算としての、動き検出(ME)、動き補償(MC)、直交変換(DCT または整数変換)、量子化(Q)、可変長符号化(VLC または CABAC/CAVLC)、更に H.264/AVC ではフレーム内予測(IPC)、ループフィルタ(LF)などを実行する実行を行うマクロブロックレイヤー、(3)これらの MB 処理に不可欠なデータを外部の高速メモリと授受を実行するデータレイヤーから構成される。名称は各種あるが、基本的な考えは変わらない。コントロールレイヤーは通常組込み CPU と内蔵ソフトウェア(ファームウェア)として実現され、マクロブロックレイヤーとデータレイヤーは特定用途向け回路として実現されることが多い。ただ、図 13・3 に示すように、マクロブロックレイヤーを専用ハードブロックと複数の専用 AV(ビデオとオーディオ)向け DSP で構成するアーキテクチャ(DoMiNo)もある 9.

映像品質と消費電力(周波数に比例)の考え方は、本アーキテクチャにおける各マクロブロックに何サイクル(チップなどの周波数として)までかけられるかに大きく依存しており、

図 13・2 H.264/AVC アルゴリズムとマクロブロックパイプラインアーキテクチャ

図 13・3 専用ハードと複数 AV 向け DSP によるアーキテクチャ (DoMiNo)

民生用か放送プロ用かの大きな違いにもなっている。1080i(1920×1080)の処理を考えた場合,マクロブロック MB ( $16 \times 16$  ピクセル)は、1 フレーム当たり横 120 個×縦 68 個で 8160 MB 個、1 秒に 30 フレーム処理するためには,毎秒 244800 MB 個を処理しなければならない。100 MHz の周波数のチップであれば、1 MB の処理にかけられるサイクルは約 400 サイクル/MB、200 MHz であれば約 800 サイクル/MB となる。近年の多くの民生(カメラ)用の専用チップは、 $400 \sim 800$  サイクル/MB で設計されており、1080i で 1 W を切るような設計となっている。レート制御のハードウェア化も含め,映像品質はこのサイクル内に収まる程度のハードウェア実装の範囲となる。

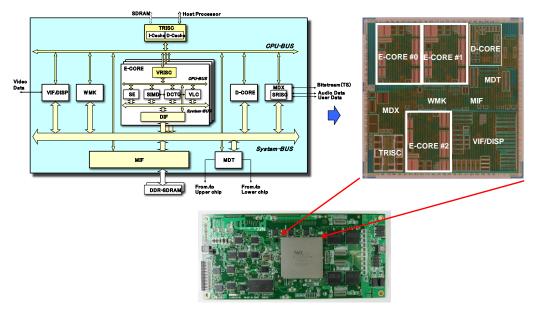

これに対して放送プロ用のチップは、MPEG-2 や H.264/AVC が有する映像品質の潜在能力を可能な限り引き出すため、民生と比較して数倍程度のサイクル数を前提とし、プレ解析による統計情報利用、広大な探索範囲や高度なモード判定、プレ・ポストフィルタ、符号化情報の継承など、映像品質の改善のための各種手法が搭載されている「<sup>10</sup>,11]。このため放送プロ用の実装では、複数の専用チップを利用した構成や、複数の専用コアをオンチップに搭載した構成を前提に、専用チップや専用コアを直接活用できるマルチストライプ並列方式(領域分割方式)の並列エンコーダの構成を採用している。それぞれ世界初を実現した地上デジタル放送の基幹網装置用の MPEG-2 チップ(VASA)のマルチコア実装のブロック構成とチップ写真を図 13・4 に、IP デジタル放送の基幹網装置用の H.264/AVC チップ(SARA)のブロック構成とチップ写真とマルチチップ実装を図 13・5 に示す。また、これらのチップやモジュールを搭載した各種の放送プロ用装置 「2½」「3)が実際の地上デジタル放送や IP デジタル放送を支えている。

**図 13・4** MPEG-2 チップ (VASA) のマルチコア実装

図 13・5 H.264/AVC チップ (SARA) のマルチチップ実装

## 13-2 映像符号化ソフトウェア

(執筆者:長沼次郎) [2013年3月受領]

映像符号化のソフトウェア実現では、対象となる映像符号化標準の処理アルゴリズムのもつ並列性を如何に実現し、ソフトウェアとして高速動作が可能なようにマイクロプロセッサヘマッピングするかが設計問題である。Intel に代表されるマイクロプロセッサの高速化 <sup>14), 15)</sup> は、表 13・1 に示すように、(1)パイプライン動作による動作周波数の向上 (GHz)、(2)スーパスカラー方式(命令並列)による1命令当たりのサイクル数の低減化 (CPI)、(3) MMX や SSEなどのマルチメディア命令(データ並列)による同時データ演算実行数の向上の歴史であった。更に、性能向上は動作周波数から(4)チップ内のコア数の向上へと大きく変化している。GHz や CPI の変化はプログラム自体の変更は必要ないが、チップ内のコア数の変化は、データ並列とともに、コア数を有効に利用したマルチスレッド・マルチコアなどの並列プログラミング <sup>16)</sup> による並列ソフトウェアの考え方が重要になる。

| 高速化の技法                | 高速化の概要                     |

|-----------------------|----------------------------|

| 動作周波数の向上              | 1秒間に実行可能なクロックサイクル数(GHz)の増加 |

| 命令並列数の向上              | 1命令当たりのサイクル数CPI)<br>の低減    |

| データ並列数の向上             | 1命令当たりの同時データ演算実<br>行数の増加   |

| マルチスレッド・マルチコア数の<br>向上 | 同時に実行可能な並列プログラム処理)の増加      |

表 13・1 マイクロプロセッサの高速化

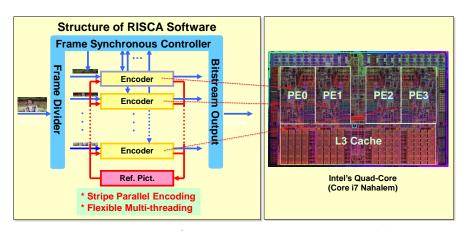

映像符号化のソフトウェア実現では、MPEG-2 や H.264/AVC の要素演算としての、動き検出 (ME)、動き補償 (MC)、直交変換 (DCT または整数変換)、量子化 (Q)、可変長符号化 (VLC または CABAC/CAVLC)、更に H.264/AVC ではフレーム内予測 (IPC)、ループフィルタ (LF) などの高速化は必須であり、特に、高速化が必要な探索や直行変換やフィルタなどのデータ構造の最適化と、MMX や SSE などのデータ並列を活用してミクロな並列処理により高速化を図る。一方、マルチスレッド・マルチコア並列を活用したマクロな並列処理(並列エンコード)による高速化の考え方として、前述のマルチストライプ並列方式が有効である。世界初のソフトウェアによる H.264/AVC フルハイビジョンエンコードのリアルタイム処理を実現した並列ソフトウェアの構成を図 13・6 に示す <sup>17)</sup>、オリジナルの映像は、まず複数スライスで分割され、次に各複数スライスの映像をチップ内のコアへマッピングして並列処理し、最後に一つのストリームに統合される。並列処理されている各複数スライス映像の複雑度や発生符号量をフィードバックして、次フレームのレート制御に用いて、フレーム内の映像領域のばらつきによる符号量配分の最適化を実現している。なお、デコード動作もほぼ同様の考え方で並列デコードできる。映像のエンコード・デコード処理とともに、オーディオのエンコード・デコード処理、IP パケットの送受信処理も含め、フルハイビジョン

H.264/AVC テレビ電話ソフトウェア (RISCA264-HD) として, 市販パソコンによる双方向の リアルタイム動作を実現している.

図 13・6 マルチストライプ方式の並列ソフトウェア (RISCA264-HD) の構成

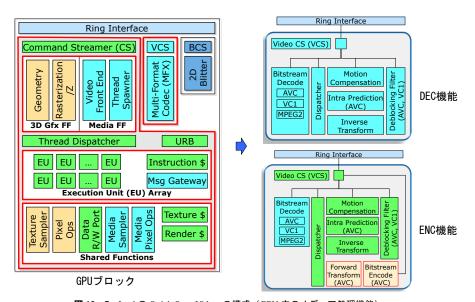

図 13・7 Intel の Quick Sync Video の構成(GPU 内のメディア処理機能)

なお、将来の映像符号化のソフトウェア実現で見逃せないのが、マイクロプロセッサの高 機能化の流れの中で、グラフィック処理機能(GPU 相当)やメディア処理機能などのハード ウェアアクセラレータのマイクロプロセッサのチップ本体への搭載である. Intel の最新マイ クロプロセッサ, Sandy-Bridge 以降では Quick Sync Video 18) と呼ばれる, MPEG-2 や H.264/AVC などの動画のハードウェアによるエンコード/デコード支援機能が付加されている. 詳細には、デコード機能は完全な専用ハードウェアを搭載し、図 13・7 に示すように、エンコード機能に関しては専用ハードウェアとグラフィックス共用のプログラマブルハードウェアを用いて実現している. 純粋にソフトウェアによる実装と比較して、数倍の高速化を達成するとともに、CPU の他処理への有効利用を可能とする. 今後の映像符号化のハードウェア/ソフトウェア実現のトレンドを大きく変える可能性がある.

## ■参考文献

- 1) ISO/IEC13818-1/2/3 International Standard: Information Technology, 1994.

- 2) ISO/IEC14496-1/2/3 International Standard: Information Technology, 2003.

- 3) HDV: http://www.sony.jp/products/Professional/c\_c/hdv/products/hdv.html

- 4) AVCHD: http://www.avchd-info.org/index.html

- J. Rattner, "Cool Codes for Hot Chips: A Quantitative Basis for Multi-core Design," Hotchips2006, Keynote1, 2006.

- 6) D. Pham, S. Asano, M. Bolliger, M. N. Day, H. P. Hofstee, C. Johns, J. Kahle, A. Kameyama, J. Keaty, Y. Masubuchi, M. Riley, D. Shippy, D. Stasiak, M. Suzuoki, M. Wang, J. Warnock, S. Weitzel, D. Wendel, T. Yamazaki, K. Yazawa, "The Design and Implementation of a First-Generation CELL Processor," ISSCC2005, pp.184-185, 2005.

- M. Ikeda, T. Kondo, K. Nitta, K. Suguri, T. Yoshitome, T. Minami, J. Naganuma, and T. Ogura, "Three-layer Cooperative Architecture for MPEG-2 Video Encoder LSI," IEICE Trans. Electronics, vol.E83-C, no.2, pp.170-178, 2000.

- M. Ikeda, H. Iwasaki, K. Nitta, T. Onishi, T. Sano, A. Sagata, Y. Nakajima, M. Inamori, T. Yoshitome, H. Matsuda, R. Tanida, A. Shimizu, K. Nakamura, and J. Naganuma, "Professional H.264/AVC CODEC Chip-set for High-quality HDTV Broadcast Infrastructure and High-end Flexible CODEC Systems," Hotchips2007, 2007.

- 9) "DoMiNo: Network Media Processor," LSI Logic, 2006.

- H. Iwasaki, J. Naganuma, K. Nitta, K. Nakamura, T. Yoshitome, M. Ogura, Y. Nakajima, Y. Tashiro, T. Onishi,

M. Ikeda, and M. Endo, "Single-chip MPEG-2 422P@HL CODEC LSI with Multi-chip Configuration for Large Scale Processing beyond HDTV Level," IEEE Trans. VLSI, vol.15, no.3, pp.1055-1059, 2007.

- 11) K. Nitta, H. Iwasaki, T. Onishi, T. Sano, A. Sagata, Y. Nakajima, M. Inamori, R. Tanida, A. Shimizu, K. Nakamura, M. Ikeda, and J. Naganuma, "An H.264/AVC High422 Profile and MPEG-2 422 Profile Encoder LSI for HDTV Broadcasting Infrastructures," IEICE Trans. Electronics, vol.E95-C, no.4, pp.432-440, 2012.

- 12) 長沼, "デジタル放送を支えるシステム LSI," NTT 技術ジャーナル, vol.19, no.6, pp.56-60, 2007.

- 13) 新田, 岩崎, 長沼, "H.264/AVC CODEC LSI 構成技術と IP 再送信サービスへの適用," NTT 技術ジャーナル, vol.21, no.3, pp.24-25, 2009.

- 14) ヘネシー&パターソン、"コンピュータアーキテクチャ 定量的アプローチ 第4版." 翔泳社、2008.

- 15) マイク・ジョンソン, "スーパースカラ・プロセッサ ーマイクロプロセッサ設計における定量的アプローチー," 日経 BP 出版センター, 1994.

- Y. Lin, A. Adl-Tabatabai, B. Saha, and C. Kozyrakis, "Multicore Programming: From Threads to Transactional Memory," Hotchips2006, Tutorial1, 2006.

- T.sano, T. Onishi, H. Iwasaki, K. Kamikura, and J. Naganuma, "A Software-based H.264/AVC HDTV Real-time Interactive CODEC Architecture Using Parallel Processing," International Conference on Consumer Electronics, ICCE2010, pp.467-468, 2010.

- H. Jiang, "The Intel Quick Sync Video Technology in the 2nd Generation Intel Core Processor Family," Hotchips2012, 2012.