# ■10 群(集積回路) - 4 編(メモリ LSI)

# 4章 不揮発性大容量メモリ

(執筆者:仁田山晃寛) [2010年1月受領]

### ■概要■

Code Storage Memory または Data Storage Memory として大容量のメモリ LSI を提供する不揮発性大容量メモリの最近の技術動向を概観し、今後の技術展望を論じる.

# 【本章の構成】

本編では、不揮発性大容量メモリの代表例として、NAND-flash メモリ(4-1 節)、NOR-flash メモリ(4-2 節)について述べる.

# 4-1 NAND-flash メモリ

(執筆者:吉川 進) [2008年9月受領]

NAND-flash メモリは 1987 年に発明され、大容量メモリとして今日ではデジタルスチルカメラ向けの SD カードや MP3 デコーダーの記憶媒体、USB メモリなど最新のデジタル家電において広く使用されている.

本節では NAND-flash メモリの構成,動作原理,信頼性,多値セルや,微細化に伴う問題などを説明する.

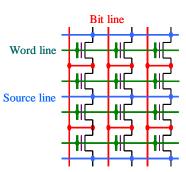

### 4-1-1 構成と特徴

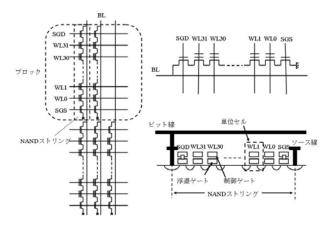

NAND-flash の単位メモリセルは電荷をためる浮遊ゲートとその電荷を制御する制御ゲートから構成される. 浮遊ゲートにためられる電荷量によりセルトランジスタの閾値が変化するがその閾値の値にデータが判別されることは他の Flash メモリと同様である. 図  $4\cdot1$  に NAND-flash メモリの構成をしめす,NAND-flash メモリは直列につながれた複数個のセルと ビット線/ソース線と,この複数個のセルとの接続を制御するトランスファーゲートによって構成される NAND ストリングが一つの構成単位になる. 書き込み,読み出し動作はページと呼ばれる同一の制御ゲートにつながる複数のセル単位で行われ,消去動作はブロックと呼ばれる同一の制御ゲートにつながる複数の NAND ストリング単位で行われる. ゲート長の最小寸法を F とすると,単位のセルあたりの面積は約 4 F² と DRAM や NOR-flash など他のメモリデバイスと比較して最少になり,このことが NAND-flash の大容量化を可能にしている.

図 4·1 NAND-flash メモリの構成

また、Page 単位でデータの書き込み、読み出しが行われることも大量のデータを取り扱うメモリとして NAND-flash が優れている点になる。また後述するように浮遊ゲートへの電荷の注入は Fowler-Nordheim トンネル電流が使われるため NOR-flash メモリと比較して書き込みのための電流が小さいといった特徴がある。

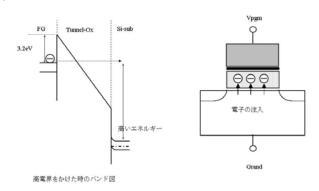

### 4-1-2 基本原理

本節では NAND-flash メモリの基礎動作原理を説明する. NAND-flash メモリでは制御ゲートに高電圧をかけるとバリアハイトの低下により、電子がトンネル可能になることによって流れる Fowler-Nordheim トンネル電流により浮遊ゲートへの電子の注入と引き出しを行い書き込み/消去をしている.

制御ゲートと基板間の容量を (Cox) 浮遊ゲートー制御ゲート間の容量を (Cipd) とすると、制御ゲートにプログラム電位 (Vpgm) をかけたときに浮遊ゲートにかかる電圧は

vfg = Cipd / (Cipd + Cox)\*Vpgm = Vpgm / (1 + Cox/Cipd)

となる. この式からわかるように Cox に対する Cipd の比率が大きいほど、一定の Vfg を与えるために必要な Vpgm の値が低くすることができるため、NAND-flash メモリにおいてはこの比率が重要なパラメターとなる.

図4・2 書き込み動作の原理

### 4-1-3 セル動作原理

本節では実際のデバイスでの書き込み・消去動作について説明する.

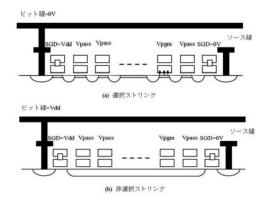

### (1) 書き込み動作

書き込みを行うセルの制御ゲートに書き込み電圧(Vpgm)を印加、それ以外のセルの制御ゲートにはこれらのセルトランジスタがオンとなるように電圧(Vpass)が印加される。選択トランジスタのゲートには Vdd の電圧が印加される。書き込み電圧(Vpgm)を印加したセルにデータが書き込まれるかどうかは、該当のセルがつながっている Bit 線の電圧に依存する。ビット線の電圧が 0 V の場合、ビット線側の選択トランジスタがオンとなり、ビット線からチャネルに対して 0 V の電位が転送される。これにより書き込みセルにおいては浮遊ゲートとチャネル間に高い電界がかかり、チャネルから浮遊ゲートに向かって電子が注入される。

一方ビット線の電圧が Vdd の場合, ビット線側の選択トランジスタがオフした状態になり, チャネルには反転層ができず, フローティング状態となる. この場合チャネルは浮遊ゲートとの間のカップリング容量により昇圧される. これにより浮遊ゲートとチャネル間に高い電界がかからないことになり電子の注入はおこらず, 書き込みが行われないことになる. このようにBit 線の電圧を変えることで, 書き込みを行うセルと書き込みを行わないセルとを制御する.

図4・3 書き込み動作

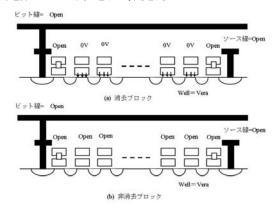

### (2) 消去動作

消去動作はブロック単位で行われる。この場合、消去されるブロックにおいては制御ゲートに 0 V が印加され、Well には約 20 V の消去電圧(Vera)が印加される。またビット線、ソース線、選択ゲートは Open となる。これにより、浮遊ゲートか Well に向かって電子が引き抜かれる。消去しないブロックにおいては制御ゲートが Open に保たれることにより浮遊ゲートは Well 間に高電界がかからず、電子の引き抜きはおこらない。

図 4・4 消去動作

### (3) 読み出し動作

読み出しは該当セルの制御ゲートに 0 V, それ以外のセルの制御ゲートと選択ゲートに各トランジスタが On する電圧を印加する. このとき読み出しするセルの浮遊ゲートに電子が高蓄積されていれば閾値が正のため電流が流れない,一方消去状態にあれば電流が流れる. この電流をセンスアンプで増幅することで,セルのデータを判定する.

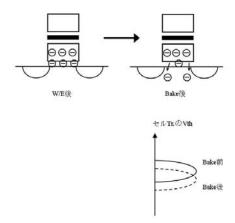

### 4-1-4 セル信頼性

浮遊ゲートへ電子の注入、引き抜きを高い頻度で繰り返すことにより酸化膜にトラップが発生する。このトラップに電荷が捕獲されることによりセルの閾値が変化することが発生する。これにより、同じ電圧を制御ゲートに印加しても、所望の閾値を得られなくなり特性の劣化が起こる。また、酸化膜中に発生したトラップに捕らえられた電荷が高温での放置によりデトラップされることで閾値が変動することが起こる。このような現象を防ぐために、1ゲート加工後の熱工程を調整しゲートバーズビークを押さえるなど、酸化膜の膜質を劣化させないプロセスの開発が行われるりなど、信頼性を保つ試みが行われている。

また、書き込み・読み出し時に制御ゲートにかかる電圧により発生する弱電界による電子 の注入がもう一つの信頼性から注意する点である。

これらの信頼性など不良ビットの発生の対策も含め誤り訂正コードを演算し、パリティビットに誤り訂正コードを書き込んでいる.

図 4.5 Bake によるデトラップとセル閾値の変動

#### 4-1-5 多値セル

今日の NAND-flash メモリにおいては単位セルに二つのデータを保持する,多値セルが主流になっている.この技術により,より大容量の記憶素子が実現されている.最近ではさらに多値化を進めた単位セルあたり 3 値 $^{21}$  や4 値 $^{31}$  を実現することでより大容量のメモリを実現する試みも発表されている.

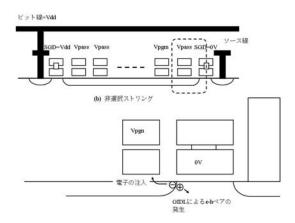

#### 4-1-6 微細化に伴う問題とその対策

微細化に伴い,浮遊ゲート間の距離が小さくなり,いくつかの懸念点が顕著になってきている.その一つに浮遊ゲート間の寄生容量の影響がある.この寄生容量により書き込んだセルのしきい値が隣接するセルの書き込み動作により変動することが特に多値セルの場合の問題となる  $^4$ . 対策の一例として浮遊ゲート間にエアギャップを作ることによりこの寄生容量を抑え提案 $^5$  もなされている.

問題の二つ目として、ソース線側の選択ゲート横のセルの書き込みを行うときに、高電圧にブーストされた拡散層において、0 V に保たれた選択ゲート直下で GIDL 電流を発生される。この電子が横方向の電界で加速され、浮遊ゲートに注入される問題が指摘されている<sup>6</sup>.この問題は微細化が進むとともに横方向の寸法が縮小される、横方向の電界が高くなることで顕著となる。この対策としてソース線側の選択ゲートとセルの間にダミーのセルを追加、その制御ゲートに印加する電圧を書き込み電圧より低くすることで GIDL を抑えることが提案されている<sup>7,8</sup>).

図 4.6

### ■参考文献

- D.-C. Kim, et. al., "A 2 Gb NAND Flash Memory with 0.044 μm Cell Size using 90 nm Flash Technology," pp.919-922, IEDM, 2002.

- Y. Li, et. al., "A 16 Gb 3b/Cell NAND Flash Memory in 56 nm with 8 MB/s Write Rate," pp.506-508, ISSCC, 2007.

- 3) N. Shibata, et. al., "A 70 nm 16 Gb 16-Level-Cell NAND Flash Memory," VLSI Symp., pp.190-191, 2007.

- M. Ichige, et. al., "A novel self-aligned shallow trench isolation cell for 90 nm 4 Gbit NAND Flash EEPROM's, VLSI Symp., pp.89-90, 2003.

- K. Tsukamoto, et. al., "An Advanced Air Gap Process for MLC flash memories reducing Vth interference and realizing high reliability," SSDM, pp.294-295, 2006.

- 6) J.D. Lee, et. al., "A NEW PROGRAMMING DISTURBANCE PHENOMENON IN NAND FLASH MEMORY BY SOURCE/DRAIN HOT-ELECTRONS GENERATED BY GIDL CURRENT," pp.31-33, NVSMW. 2006.

- K.T. Park, et. al., "Scalable Word line Shielding Scheme using Dummy Cell beyond 40nm NAND Flash Memory for Eliminating Abnormal Disturb of Edge Memory Cell," SSDM, pp.298-299, 2006.

- K. Kanda, et. al., "A 120 mm<sup>2</sup> 16 Gb 4-MLC Flash Memory with 43 nm CMOS Technology," pp.430-431, ISSCC, 2007.

# 4-2 NOR-flash メモリ

(執筆者:成毛清実) [2008年10月受領]

NOR-flash は、NAND-flash に比べて集積度は劣るが、データのランダム読み出し速度については勝る.この高速ランダム読み出しが可能である特徴を生かし、電子機器、携帯電話、デジタルカメラなどのプログラムを格納するメモリとして多用されている.

この節では、フローティングゲートを有する構造で、書き込みに Channel-Hot-Electron 注入を使う NOR-flash を中心に解説し、最後にその他の NOR-flash も簡単に紹介する.

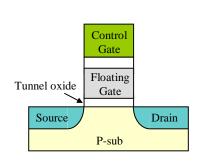

# 4-2-1 セル構造とメモリセルアレー

NOR-flash セルの断面構造を図 4·7 に示す. ソース拡散層とドレイン拡散層に挟まれたチャネル上にトンネル酸化膜を介してフローティングゲートとコントロールゲートの積層ゲートがある. フローティングゲートは絶縁膜で覆われ、周囲と電気的に分離されている.

セルアレー配置を図 4·8 に示す. 各セルがドレインコンタクトと, ソースコンタクトを有し, ビット線とソース線間に並列接続されている.

図 4·7 NOR-flash セル断面構造図

図 4.8 セルアレー配置図

### 4-2-2 動作モード

書き込みは、ドレイン端で Channel-Hot-Electron をフローティングゲートへ注入することで行う。 消去は、フローティングゲートから基板に向けて電子を F-N トンネル放出することで行う。 フローティングゲート内の電子の数でコントロールゲートから見たしきい値電圧が変化することを利用して情報を読み出す。使用電圧の例を表  $4\cdot1$  に示す。

|      | 消去                     | 書き込み  | 読み出し |

|------|------------------------|-------|------|

| 基板   | ~10 V                  | 0 V   | 0 V  |

| ソース  | 基板電位                   | 0 V   | 0 V  |

| ドレイン | 基板電位                   | ~5 V  | ~1 V |

| ゲート  | $\sim$ $-10 \text{ V}$ | ~10 V | ∼5 V |

表 4·1 動作電圧例

#### (1) 書き込み (雷子注入) 動作

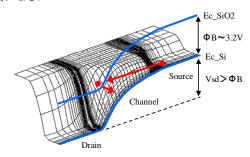

Channel-Hot-Electron 注入とは、図 4・9 に示すように、ドレイン電圧によりドレイン端の酸化膜のエネルギー障壁を引き下げて、チャネルを流れる電子の一部を酸化膜のエネルギー障壁を越えてフローティングゲートへ注入するものである。散乱でエネルギーを失わずに、フローティングゲート方向に向きを変えた Lucky-electron が注入される. 1 us 程度の速い書き込み速度を得るためには、ソースードレイン間には酸化膜のエネルギー障壁に相当する 3.2 V以上の電位差が必要になる.

図 4·9 NOR-flash 書き込み時の Si 表面のエネルギーバンド状態

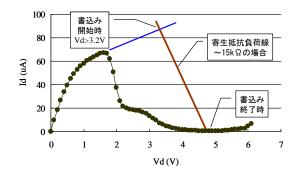

図  $4\cdot 10$  に単体セルの One-shot-program の例を示す. ドレイン電圧の上昇に伴いドレイン電流が増加し、その後フローティングゲートへ電子注入が起こり、電流が減少する. 電圧のスイープ速度が遅いため、約 2 V のドレイン電圧で電子注入が観測されているが、速い書き込み速度を得るには、3.2 V 以上のドレイン電圧が必要である. アレー配置の場合には、書き込みドレイン電流に加えてビット線リーク電流と寄生抵抗(カラムセレクト Tr の抵抗、ビット線抵抗、他)による電位降下を考慮する必要がある. デザインや使用材料で異なるが、通常ビット線入力端の電圧は約 5 V で設計されている. セルが書込まれるとドレイン電流が減り、寄生抵抗による電位降下が減るので、ドレインにはビット線入力端の電圧が印加されることになる. セルのドレインは、この電圧に耐えなければない.

図 4·10 NOR-flash の One-shot-programming 例

#### (2) 消去 (雷子放出) 動作

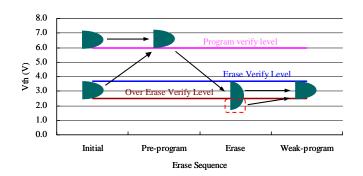

消去はブロック単位で行う.単位ブロックの大きさは、2値品では512 kbit、多値品では1 Mbit や2 Mbit で、仕様により異なる. NOR-flash では、過消去(しきい値電圧が低すぎる)セルが存在してはならない. 過消去セルは、書き込み時にビット線リークを引き起こし、書き込み特性の悪化を招くからである. このため、NOR-flash の消去シーケンスは、過消去セルを作らない工夫がなされている. 図4・11 にそのシーケンス例りを示す. 最初 Pre-Program で、消去ブロック内の全セルを高いしきい値レベルに書き揃える. 次いで Erase で、トンネル消去とベリファイを繰り返しながら、ブロック内の総てのセルが Erase-Verify-Level 以下になるまで消去を行う. このとき、消去の速いセルは過消去状態になっている. Weak-program で、この過消去セルを Over-Erase-Verify-Level 以上に書き戻しを行い、過消去セルを無くす.

図 4·11 NOR-flash の消去シーケンス

#### 4-2-3 NOR-flash 微細化のトレンド

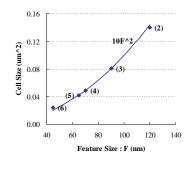

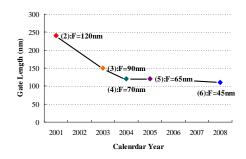

微細加工寸法 F 値とセルサイズの関係を図  $4\cdot 12$  に示す。セルサイズは、ほぼ 10  $F^2$  の関係を保ってスケーリングされている。一方、ゲート長は図  $4\cdot 13$  に示すように、微細化が止まった感がある。これは、前述したように、Channel-Hot-Electron 書き込みでは、セルのソースードレイン間に約 5 V の耐圧が必要で、これがゲート長微細化の律束要因になっている。

図 4・12 セルサイズトレンド

図 4・13 ゲート長トレンド

#### 4-2-4 その他の NOR-flash

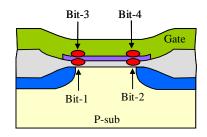

NROM (Mirror-bit) か セル (図  $4\cdot14$  参照) は、通常の NOR-Flash と同様に Channel-Hot-Electron 書き込み方式を使うが、セルを Virtual-Ground-Array 型に配置してセル内のコンタクトを省き、高集積度を実現している。また電荷蓄積層にトラップ膜を使い、電荷捕獲領域をチャネルのドレイン端とソース端の 2 ヶ所に設け、電荷量制御と合わせて多値化を図っている。

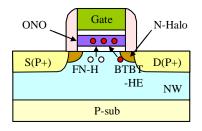

B4-flash 8) セル(図  $4\cdot15$  参照)は、新規書き込み方式を使う Pch デバイスである。コントロールゲートに正電圧、ビット線に(相対的に)負電圧を印加して、その交点にあるゲート直下のドレイン端で Pch Band-to-band トンネルによる Pch Hot-Electron を発生させ、 Pch Back-bias のアシストを使って、 Pch Hot-Electron を電荷蓄積層(この例では Pch ONOの 空化膜)に注入する. Pch Hot-Electron の発生にソースードレイン間の電位差が不要なので、ゲート長の微細化に向き、 Pch L= 60 nm を実現している。また、 Pch Channel-Hot-Electron 書き込み方式に比べてプログラム電流が少ないので、 通常 Pch NOR-flash よりも多くの bit の同時書き込みが可能である。

図 4·14 NROM (Mirror bit) セル

図 4·15 B4-flash セル

#### ■参考文献

- 1) H. Shiga, et. al., VLSI Circuits Dig., C4-2, 1999.

- 2) Y. Song, et. al., IEDM Tech. Dig., 2-4, 2001.

- 3) Y. Song, et. al., VLSI Tech. Dig., T7B-2, 2003.

- 4) C. Park, et. al., VLSI Tech.Dig., T23-1, 2004.

- 5) G. Servalli, et. al., IEDM Tech. Dig., 35-1, 2005.

- 6) R. Fastow, et. al., VLSI-TSA Dig., T53A, 2008.

- 7) B. Eitan, et. al., IEDM Tech. Dig., 22-1, 2005.

- 8) S. Shukuri, et. al., VLSI Tech. Dig., T3-1, 2006.