# 6章 ΔΣ変調回路

(執筆者:安田 彰) [2009年8月受領]

#### ■概要■

$\Delta\Sigma$ 変調器は、アナログ回路特性がアナログーディジタル変換特性に及ぼす影響が小さいことから高精度 A/D 変換器の実現手段として広く用いられるようになってきている。  $\Delta\Sigma$ 変調器では内部 ADC 出力を入力段に帰還することで、内部 ADC で生じる量子化雑音の低域成分を帰還回路のループ利得分低減させる。これをノイズシェーピングと呼ぶ。また、A/D 変換する周波数帯域の 2 倍よりも高い周波数でサンプリングするオーバーサンプリングを行いノイズシェーピングで低減された周波数領域のみを A/D 変換出力とすることにより、高精度変換が実現できる。 ループフィルタに通常積分器を用いるが、積分器を多段接続しループフィルタの利得を向上させることで、ノイズシェーピング特性が急峻になり量子化雑音を低減することが可能である。しかし、3 次以上のループフィルタを用いた場合は、内部 ADC で生じる量子化雑音の影響によりループが不安定になり、ループ利得を下げなければ安定化できない。

$\Delta \Sigma$ 変調器の構成方法にはシングルステージ型と、基本 $\Delta \Sigma$ 変調器を多段に接続し 1 段目の量子化雑音を後段の変調器で変換することで精度を向上させるカスケード型がある。カスケード型では、2 次以下のループフィルタを用いた $\Delta \Sigma$ 変調器を各段に用いることにより、安定性を損なわずに高次のノイズシェーピング特性を実現できる。

上記の積分器に代え共振器を用いることでノイズシェーピングにより量子化雑音を低減する周波数を DC 以外に設定することが可能となる。これをバンドパス型 $\Delta\Sigma$ 変調器と呼ぶ。バンドパス型では、ヘテロダイン受信器のような中間周波数信号を直接 A/D 変換することが可能である。

ΔΣ変調器の回路実現方法としては、ループフィルタをスイッチトキャパシタ (SC) 回路などの離散時間回路で実現する DT 型と RC 積分器などの連続時間回路で実現する CT 型方法がある. SC 回路は比較的容易に回路実現でき、クロックジッタの影響も小さいことから広く用いられている. 一方、連続時間回路は SC 回路に比較して高速動作が可能であり、高速変換が求められる場合に用いられるようになってきている. CT 型はサンプリングがループフィルタに後置される内部 ADC で行われるため、変調器がアンチエリアス特性を持っている. しかし、ジッタの影響が大きい.

$\Delta\Sigma$ 変調器は DAC を構成することも可能である。変調器をディジタル回路で実現し、内部量子化器出力を内部 DAC でアナログ信号に変換することで、ノイズシェーピング特性を持った出力を得ることができる。

#### 【本章の構成】

本章では以下に関して、その基礎理論、特性、実現方法について述べる.

- 6-1 ΔΣ変調器

- 6-2 カスケード型ΔΣ変調器

- 6-3 DT 型ΔΣ A/D 変換器

6-4 CT 型ΔΣ A/D 変換器

6-5 バンドパス型ΔΣ A/D 変換器

6-6 ΔΣ型 D/A 変換器

### 6-1 ΔΣ変調器

(執筆者:安田 彰) [2009年8月受領]

#### シングルステージ型ΔΣ変調器

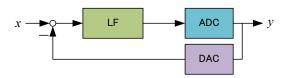

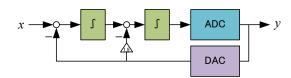

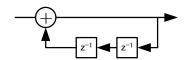

$\Delta \Sigma$ 変調器 <sup>1)</sup> の基本形となるシングルステージ型 $\Delta \Sigma$ 変調器 (1stgDSM) のブロック図を**図 1·1** に示す <sup>2)</sup>. 1stgDSM は,ループフィルタ(LF),内部 ADC,内部 DAC,及び減算器により構成 される. ADC で量子化された出力信号 y は入力にフィードバックされ,これによって DC 入力 に対しては x と y が一致するように動作する. x – y ,すなわち変換による誤差が積分器の入力 となり,ループはこの誤差をフィルタした値が 0 となるように制御される.

図 1 · 1 1 次ΔΣ変調器

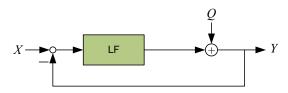

図  $1\cdot 2$  に 1stgDSM の等価回路を示す.この図において,Q は内部 ADC における量子化雑音を示す.この等価回路の z 領域における伝達関数は,

$$Y(z) = \frac{H(z)}{1 + H(z)}X(z) + \frac{1}{1 + H(z)}Q(z)$$

(1 · 1)

となる. ここで、Y(z) は出力信号、X(z) は入力信号、Q(z) は量子化雑音、H(z) はループフィルタの伝達関数である. 式( $6\cdot 1$ ) より、量子化雑音には伝達関数がかかっており、低域に大きな利得を有する H(z) を用いれば DC 付近の雑音が低減されることが分かる. これをノイズシェーピングと呼ぶ. また、入力信号から出力信号への伝達関数を信号伝達関数 STF、量子化雑音から出力への伝達関数を雑音伝達関数 NTF と呼ぶ.

**図1・2** 1次ΔΣ変調器の線形モデル

ここで, 量子化雑音 Q(z) が白色雑音と仮定すると, 信号帯域内雑音は,

$$N^{2} = \left| Q(\omega) \right|^{2} \frac{1}{2\pi} \int_{-\frac{CSR}{OSR}}^{\frac{\pi}{OSR}} \left| H(\omega) \right|^{2} d\omega \tag{1.2}$$

と表される. ここで、 $OSR = f_s/(2f_B)$  はオーバーサンプリング比、 $f_s$ はサンプリング周波数、 $f_B$ は信号帯域である.

ループフィルタに積分器を用いた場合  $H(z) = z^{-1}/(1-z^{-1})$ となり、このとき出力は、

$$Y(z) = z^{-1}X(z) + (1 - z^{-1})Q(z)$$

(1 · 3)

となる.量子化雑音 Q(z)には( $1-z^{-1}$ )がかかり,DC における量子化雑音の影響はなくなる.これは直流に対しては無限の精度を実現できることを示している.また,サンプリング周波数 から周波数が低くなるに従いノイズシェーピング項( $1-z^{-1}$ )の値は-20 dB/dec で減少することから,これを 1 次ノイズシェーピングと呼ぶ.また,このとき式( $1\cdot 2$ )は, $H(\omega)$  に  $1-e^{-j\omega}$ , $z^{-1}$ に  $e^{-j\omega}$ を代入すると,

$$N^{2} = |Q(\omega)|^{2} \frac{1}{2\pi} \int_{\frac{\partial SR}{\partial SP}}^{\frac{\pi}{\partial SR}} 4\sin^{2}\left(\frac{\omega}{2}\right) d\omega = |Q(\omega)|^{2} \frac{2}{\pi} \left\{ \frac{\pi}{OSR} - \sin\left(\frac{\omega}{2}\right) \right\}$$

(1 · 4)

となる. オーバーサンプリング比が高い場合  $\pi/OSR \ll 1$ となり,

$$N^2 \approx |Q(\omega)|^2 \frac{1}{3\pi} \left(\frac{\pi}{OSR}\right)^3$$

(1 · 5)

$$N^2 \approx \frac{\pi^2}{9(OSR)^3} \tag{1.6}$$

となる. 入力信号がフルスケールの正弦波で振幅がMとすると、出力信号パワーは $M^2/2$ である. したがって、最大の信号対雑音比SONRは次のようになる.

$$SQNR = \frac{9M^2(OSR)^3}{2\pi^2} \tag{1.7}$$

1 次ΔΣ変調器では、オーバーサンプリング比の 3 乗で SQNR が改善し、オーバーサンプリング比を 2 倍にすることにより SQNR が 9 dB 改善される. オーバーサンプリング比が 128、内部 ADC が 1 bit の場合の SNR は、59.8 dB となる.

1stDSM では、ループフィルタの次数を上げることにより、そのノイズシェーピング特性を 急峻にすることができ、SQNR を改善することができる。2 次ΔΣ変調器では、オーバーサンプ リング比の 5 乗で SQNR が改善し、オーバーサンプリング比を 2 倍にすることにより SQNR が 15 dB 改善される。

これよりもループフィルタの次数を上げれば更に SQNR が改善することになるが,内部 ADC を 1 bit とした場合は,3 次以上の場合ループが内部 ADC の非線形特性により不安定となる.これを解決するには,ループ全体の極配置により安定化を図るか,内部 ADC のビット数を上げる必要がある.極配置により安定化を図った場合,ノイズシェーピング特性が犠牲になる点に注意する必要がある.

# 6-2 カスケード型ΔΣ変調器

(執筆者:安田 彰) [2009年8月受領]

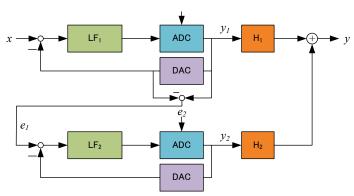

内部 ADC で発生する量子化雑音を別の ADC で変換し、この出力を用いて出力コード中の量子化雑音の低減を図る方法が考えられる。図  $2\cdot 1$  に示すカスケード型 $\Delta\Sigma$ 変調器(MASH)では、1段目の ADC 出力  $y_1$  から ADC の入力信号を減算し量子化雑音信号  $E_1$  を生成し、 $E_1$  を 2段目の $\Delta\Sigma$ 変調器で量子化する。1段目の出力  $y_1$  を 2段目の出力  $y_2$  で補正する。ここで、図  $2\cdot 1$ のように線形モデルを用いて各出力を記述すると以下のようになる。

$$Y_{1} = STF_{1}(z)X(z) + NTF_{1}(z)E_{1}(z)$$

$$Y_{2} = STF_{2}(z)E_{1}(z) + NTF_{2}(z)E_{2}(z)$$

$$Y = H_{1}(z)Y_{1}(z) + H_{2}(z)Y_{2}(z)$$

(2 · 1)

ここで、次の条件が満たされれば初段の量子化雑音 E<sub>1</sub>を相殺することが可能となる.

$$NTF_1(z)H_1(z) - STF_2H_2(z) = 0$$

(2 · 2)

これを満たすには,

$$H_1(z) = STF_2(z), H_2(z) = NTF_1$$

(2 · 3)

とすればよい. この場合, 全体の出力は,

$$Y = STF_1(z)STF_2(z)X(z) + NTF_1(z)NTF_2(z)E_2(z)$$

(2 • 4)

となる. 初段及び2段目が2次ΔΣ変調器で構成される場合, 通常これらの伝達関数は

$$STF_1(z) = z^{-2}$$

,  $STF_2(z) = z^{-2}$ ,  $NTF_1(z) = (1 - z^{-1})^2$ ,  $NTF_2(z) = (1 - z^{-1})^2$

で与えられ,全体の出力は,

$$Y(z) = z^{-4}X(z) + (1 - z^{-1})^4 E_2(z)$$

(2 · 5)

**図2・1** カスケード型ΔΣ変調器

となる. カスコード型 $\Delta\Sigma$ 変調器の雑音特性は、2段目の量子化雑音に各段のノイズシェーピング特性を乗じたものと等しくなる. 一方、 $\Delta\Sigma$ 変調器ループの安定性は、各段で考慮すればよく、この場合、それぞれ2次の安定性と同等になる.

アナログ回路でカスコード型 $\Delta\Sigma$ 変調器を実現する場合,アナログ回路で決まる  $NTF_1$  とディジタル回路で実現する  $H_2$  とのマッチングが問題となることに注意する必要がある.初段を 2 次とすることにより,この影響が低減される.

# 6-3 DT 型ΔΣ A/D 変換器

(執筆者:安田 彰) [2009年8月受領]

$\Delta\Sigma$  A/D 変換器は,入力アナログ信号をディジタル信号に変換するため離散時間系システム(Discrete Time System)であり,離散時間回路として実現した場合 DT 型 $\Delta\Sigma$  A/D 変換器と呼ばれる.離散時間回路を実現する回路方式として通常スイッチトキャパシタ(SC)回路が用いられる.

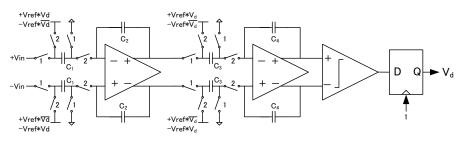

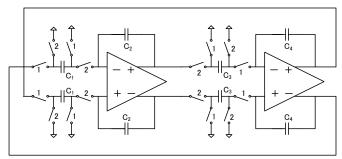

2次ΔΣ変調器をスイッチトキャパシタ回路で実現した回路図を図3・1 に示す. 直列接続された SC 積分器でループフィルタ, コンパレータ, D フリップフロップ (D-FF) で内部 1-bit A/D 変換器を構成している. 内部 DAC は, SC 積分器に接続された SC 回路で実現される. D-FF 出力にデシメーションフィルタ (DF) を後置し, 帯域外の雑音を抑圧後ダウンサンプリングし最終出力を得る. ここで用いる OPAMP には, 負荷がキャパシタであるため通常トランスコンダクタ型が用いられる場合が多い.

図3・1 2次 DT 型ΔΣ A/D 変換器

OPAMP の利得が有限の場合,SC 積分器の特性が理想特性から外れ, $C_1 = C_2$  の場合 DC の極が 1-1/A に移動する.ここで,A は OPAMP の直流利得である.これによりノイズシェーピング特性が劣化するが,この影響は小さく A> OSR であれば問題とはならない.しかし,A が小さい場合,OPAMP の非線形性により生じる歪みが問題となるため,OPAMP の利得は,歪みにより決まり,これは回路シミュレーションにより決定する必要がある.

DT型 $\Delta\Sigma$  A/D 変換器の特徴は、回路素子値の影響が小さく容易に高精度特性を得られる点にある。SC 回路では積分器の利得などがキャパシタ比で決まるため、素子値の絶対値精度への要求が低い。一方、入力部で SC 回路によりサンプリングを行うため、MOS スイッチなどの熱雑音は  $1/f_s$ に折り返し kT/C 雑音が生じる。ここで、 $f_s$ はサンプリング周波数である。入力部のキャパシタ値は、雑音に対する要求を満足するように選ぶ必要がある。これ以外の雑音源として帯域内の OPAMP からの熱雑音や 1/f 雑音がある。2 段目で生じるこれらの雑音の入力換算値は、初段の積分器の利得分の 1 になるため、オーバーサンプリング比が高い場合、通常問題とならない。積分器の別な構成方法としては、スイッチトカレント回路や S/H を用いる方法などがある。

# 6-4 CT 型ΔΣ A/D 変換器

(執筆者:安田 彰) [2009年8月受領]

$\Delta\Sigma$  A/D 変換器のループフィルタを連続時間回路で実現したものは CT 型 $\Delta\Sigma$  A/D 変換器と呼ばれる. この場合でも内部 ADC はサンプリング動作しており, $\Delta\Sigma$  A/D 変換器全体は離散時間システムである.

ループフィルタを連続時間回路として実現した場合、CT 型 $\Delta\Sigma$  A/D 変換器の最高クロック周波数は、内部 A/D 変換器及び内部 D/A の変換時間により決まる。SC 回路で実現した場合は、OPAPM のセトリング時間で決まり、この値は OPAMP のユニティゲイン周波数のおよそ 1/10から 1/5 である。したがって、CT 型は SC 回路実現に比べ 2から 4 倍高速動作が可能である。

また、CT 型 $\Delta\Sigma$  A/D 変換器では、ループフィルタは連続時間回路であるため、ここではサンプリングが行われず、ここでは折り返し雑音が生じない。サンプリングは内部 A/D 変換器で初めて行われるため、折り返し雑音に対しても一種のノイズシェーピングが実現さる。このため、CT 型はアンチエリアス特性を持っており、前置されるアンチエリアスフィルタへの要求を大幅に緩和でき、アンチエリアスフィルタを取り去ることも可能となる。

一方、CT型ループフィルタの時定数はフィルタを構成する素子の絶対値で決定される. LSI における C, R,  $g_m$ などの値は 10%程度ばらつくことがあり、時定数も大幅にばらつくことになる。また、CT 型ではサンプリング周波数の変化によりループフィルタの利得が変動する. したがって、SC 型のようにサンプリング周波数を変化させても同じ離散時間伝達特性を実現できず、サンプリング周波数により CT 型ループフィルタの係数を可変する必要がある。これらの理由から CT 型ではなんらかの時定数のチューニングが必要となる。

図 4 · 1 2 次 CT 型ΔΣ A/D 変換器

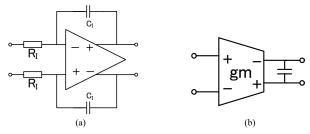

図4・2 連続時間積分器の例

2次 CT 型 $\Delta\Sigma$  A/D 変換器のブロック図を図 **4·1** に示す. ループフィルタを構成する積分器には連続時間積分器が用いられる(図 **4·2**). この積分器には、OPAMP を用いた RC 積分器やト

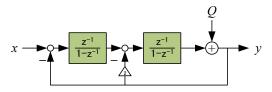

ランスコンダクタを用いた gm-C 積分器などを用いることができる。CT 型ループフィルタをサンプリング周波数  $f_s$  で離散時間システムに変換したブロック図を**図 4・3** に示す.この変換により係数が変わるため,単に CT 型ループフィルタを DT 型ループフィルタに変更すれば CT 型 $\Delta\Sigma$  A/D 変換器を DT 型 $\Delta\Sigma$  A/D 変換器をのではない点に注意する必要がある.

図4・3 図4・1と等価な離散時間変調器

# 6-5 バンドパス型ΔΣ A/D 変換器

(執筆者:安田 彰) [2009年8月受領]

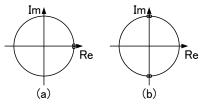

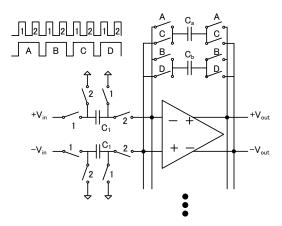

6-1 節で示したローパス型 $\Delta\Sigma$ 変調器では、ループフィルタに積分器を用いることで NTF の 零点を DC に配置していた(図 5·1(a)). バンドパス型 $\Delta\Sigma$  変調器では、図 5·1(b)のように DC 以外に配置する. NTF の零点に共振周波数を持つ共振器をループフィルタに用いることで、これを実現することができる. 図 5·1(b)のように NTF の零点を  $1/4f_s$ に配置するとループフィルタを構成しやすく、またバンドパス型 $\Delta\Sigma$  A/D 変換器に後置するディジタル直交ミキサを容易に実現できる.

図 5・1 ローパス型(a)とバンドパス型(b)の NTF

バンドパス型 $\Delta\Sigma$  A/D 変換器では、IF 信号のような狭帯域信号を直接 A/D 変換することが可能となる。中心周波数付近の量子化雑音に対してノイズシェーピング特性が実現できることから、ナイキストレート A/D 変換器を用いる場合と比較して信号帯域に対して高いオーバーサンプリング比を実現でき、高い SQNR を実現できる.

NTF の零点を 1/4  $f_s$  に配置するには, $z \to -z^2$  の変換を行うことにより実現できる.この変換により変換した共振器を図  $5\cdot2$  に示す.別の共振器の構成方法として,図  $5\cdot3$  に示した積分器を用いた方法や,図  $5\cdot4$  に示した疑 2 経路 SC 型回路がある.

図5・2 積分器を $z \rightarrow -z^2$ 変換により変換した共振器

図5・3 2つの積分器による SC 型共振器

図5・4 疑2経路 SC型 fs/4 共振器

### 6-6 ΔΣ型 D/A 変換器

(執筆者:安田 彰) [2009年8月受領]

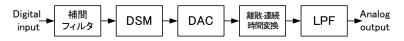

$\Delta\Sigma$ 型 D/A 変換器は、 $\Delta\Sigma$ 変調器をディジタル回路で構成し、内部量子化器の出力を内部 D/A 変換器でアナログ出力信号に変換する。  $\Delta\Sigma$ 型 D/A 変換器では、図  $6\cdot1$  示すように $\Delta\Sigma$ 変調器にインターポレーションを前置し、 $\Delta\Sigma$ 変調器のサンプリング周波数までアップサンプリングさせるとともにアップサンプリングにより生じるイメージ信号を抑圧させる。内部 D/A 変換器に後置される離散時間 LPF でノイズシェーピングされた量子化雑音を減衰させダウンサンプリングを行う場合もある。離散時間–連続時間変換器で連続時間信号に変換し、連続時間 LPF で帯域外量子化雑音及び高域の繰り返しスペクトルを減衰させる。

$\Delta\Sigma$ 型 D/A 変換器では、 $\Delta\Sigma$ 変調器はディジタル回路であるため、係数などのミスマッチがないため、変調器には様々な形式を用いることができる。

図 6・1 ΔΣ型 D/A 変換器のブロック図

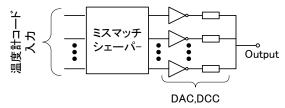

D/A 変換器では、出力の時間波形すべてが連続時間信号として出力信号精度を決定することになる。内部 DAC が多ビットの変調器を用いた方が帯域外雑音やクロックジッタの影響が小さく D/A 変換器では多ビット型が広く用いられている。しかし、多ビット内部 D/A 変換器には最終変換精度と同程度の精度が要求される。通常の LSI では、キャパシタや抵抗の値のミスマッチばらつきは 0.1%程度あり、十分な精度を確保できない。このため、ミスマッチにより生じる雑音の影響を低減させるミスマッチシェーパー<sup>3),4)</sup> が用いられる。使用するインバータをミスマッチシェーパーで選択する多ビット内部 DAC 及び離散時間-連続時間変換器 (DCC) の構成例を図 6・2 に示す。

図6・2 ミスマッチシェーパー,インバータを用いた多ビットDAC

別の DCC 実現法として、SC フィルタを用いる実現法がある。SC フィルタにより、帯域外雑音を減衰させることによりクロック間における波形のステップサイズが減少し、クロックジッタの影響、OPAMP のセトリング特性の影響を低減することが可能となる。SC フィルタの最終段には OPAMP のセトリング時間の影響を低減した直接電荷転送段 5 が離散時間-連続時間変換器として用いられる。

#### ■参考文献

- J. Murakami H. Inose, and Y. Yasuda: "A telemetering system by code modulation modulation," IRE Transactions Space Electron. Telemetry, vol.SET-8, pp.204-209, Sep. 1962.

- 2) R. Schreier and G.C. Temes: "Understanding Delta-Sigma Data Converters," Wiley-IEEE Press, 2004.

- B. Zhang and R. Schreier: "Noise-shaped multbit D/A convertor employing unit elements," IEE Electronics Letters, pp.1712-171, Sep. 1995.

- A. Yasuda, H. Tanimoto, and T. Iida: "A 100 khz, 9.6mw multibit ΔΣ DAC and ADC using noise shaping dynamic elements matching with a tree structure," IEEE ISSCC Dig. Tech. Papers, pp.64-65, Feb. 1998.

- J.A.C. Bingham: "Applications of a direct-transfer SC integrator," IEEE Transactions on Circuits and Systems, vol.31, pp.419-420, Apr. 1984.